# LCD01D DVB-S2/DVB-S2X High Speed LDPC/BCH Decoder

1 December 2021 (Version 1.04)

# LCD01D Features

#### LDPC Decoder

- Digital Video Broadcasting Second Generation (DVB–S2) and Extensions (DVB–S2X) compatible

- Nominal code rates from 1/5 to 9/10

- Data lengths from 2512 to 58192 bits

- Optional π/2 BPSK SF2, π/2 BPSK, QPSK, 8PSK, 8APSK, 16APSK, 32APSK, 64APSK, 128APSK and 256APSK demapping and deinterleaving with 11-bit inphase and quadrature two's complement input

- Optional interleaved or deinterleaved 8-bit loglikelihood-ratio (LLR) input

- Includes ping-pong input and output memories, BCH decoder and optional descrambler

- Scaled min-sum modified Gauss-Seidel low density parity check (LDPC) decoding algorithm

- Up to 323 MHz internal clock

- Up to 290 Mbit/s with 30 decoder iterations

- Up to 256 iterations

- Programmable signal points option

- Optional power efficient early stopping

- LDPC parity check and BCH error location polynomial degree output

- ~42,000 LUTs and 287 RAMB18s for Xilinx Virtex–5, Virtex–6, 7–Series, UltraScale and Ultra-Scale+ FPGAs. ~53,000 ALUTs and 436 M10Ks for Altera Cyclone V.

- Free simulation software

- Available as VHDL core for Xilinx FPGAs under SignOnce IP License. ASIC, Intel/Altera, Lattice and Microsemi/Actel cores available on request.

# Introduction

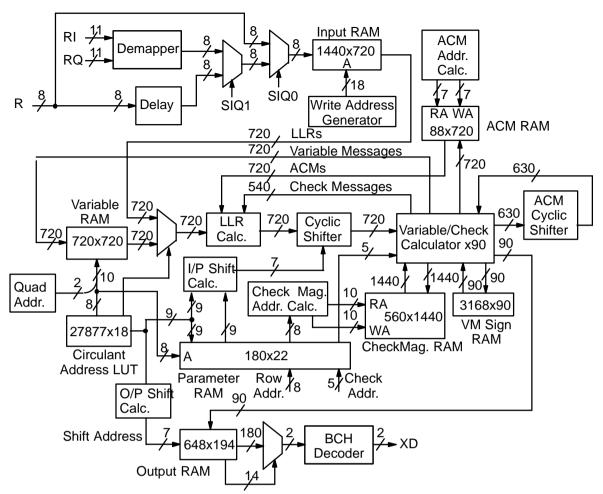

The LCD01D is a fully compatible Digital Video Broadcasting Second Generation (DVB–S2) [1] and Extensions (DVB–S2X) [2] error control decoder. It includes an optional demapper, LDPC decoder, BCH decoder and optional descrambler. Nominal LDPC code rates range from 1/5 to 9/10. Irregular repeat accumulate quasi–cyclic LDPC codes with circulant weights ranging from 1 to 4 (for the DVB–S2 codes [1]) and weight 1 (for the DVB–S2X codes[2]) are used. Circulant sizes for all codes is 360x360. There are from 5 to 140 cir-

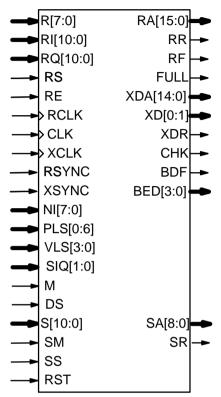

Figure 1: LCD01D schematic symbol.

culant rows and either 45, 90 or 180 circulant columns in the parity check matrix.

The check node degree is irregular with one to five different values for each code. Due to the accumulate encoding method for the parity check bits, the first row has a check degree which is one less than the following 359 rows. The average check degree varies from 3.417 to 30.

The variable node degree is irregular with two to six different values for each code. Variable degrees range from 3 to 24 for the information bits. For the parity bits, due to the accumulate encoding method used, all column's have a variable degree of 2, except for the last column which has a degree of 1.

For DVB–S2 there are two sets of LDPC codes in the standard. These are Short and Normal which have code lengths of 16,200 and 64,800 bits, respectively. For DVB–S2X, there are additional Short and Normal codes, along with Medium codes which have coded lengths of 32,400 bits before puncturing. Some of these

## Product Specification

<sup>1</sup> December 2021 (Version 1.04)

codes are shortened and punctured for VL–SNR to obtain coded lengths of 14,976, 15,390, 30,780 or 61,560 bits. For DVB–S2 there are a total of 10 Short codes and 11 Normal codes. For DVB–S2X there are an additional seven Short codes, three Medium codes and 24 Normal codes. Five codes are used in both punctured and non–punctured form, giving a total of 60 different LDPC codes.

For DVB–S2 four different modulation schemes are used; QPSK, 8PSK, 16APSK and 32APSK [1]. For 16APSK and 32APSK there are six and five different versions, respectively, formed by varying the relative levels of the signal points. For DVB–S2X there are additional  $\pi/2$  BPSK,  $\pi/2$  BPSK Spreading Factor 2 (SF2), 8APSK (2 versions), 16APSK (9 versions), 32APSK (6 versions), 64APSK (4 versions), 128APSK (2 versions) and 256APSK (5 versions) modulation schemes used [2]. This gives a total of 43 different modulation schemes. Along with 27 different bit interleaver patterns, a total of 116 different modulation and coding schemes are used.

A modified Gauss–Seidel [3] iterative message passing algorithm is used in the decoder. In each clock cycle, 90 check nodes are decoded and the variable messages (VMs) updated. Each iteration requires  $4qd_c$  clock cycles to calculate the updated VMs, where  $d_c$  is the average check degree value and q is the number of circulant rows. For calculation of the check messages (CMs), the scaled min–sum decoding algorithm [4] is used.

The LDPC decoder can achieve up to 290 Mbit/s with 30 iterations using a 323 MHz internal clock. Optional early stopping allows the decoder to reduce power consumption with no degradation in performance.

The decoder contains an input memory, VM memory, CM memory, VM sign memory, parameter memory and an output memory for the decoded data. The input and output memories are separated into two halves to allow ping–pong operation and maximum decoder speed. Separate clocks can be used for the input and output memories. As DVB–S2 LDPC codes can have circulant weights greater than one, several additional memories are also used.

An optional demapper and deinterleaver for the various modulation schemes is included. This allows 11-bit inphase and quadrature samples to be demapped into individual bit log-likelihood ratios (LLR) and deinterleaved. Alternatively, 8-bit LLR data can be input either interleaved or deinterleaved into the decoder. A BCH decoder using the Berlekamp algorithm [5] is included to clean up any residual errors from the LDPC decoder. For DVB–S2 codes, the BCH decoder can correct up to either 8, 10 or 12 errors. For DVB–S2X, up to 12 errors can be corrected. For Short, Medium and Normal codes the corresponding Galois field is  $GF(2^{14})$ ,  $GF(2^{15})$  and  $GF(2^{16})$ , respectively.

Figure 1 shows the schematic symbol for the LCD01D decoder. The VHDL core can be used with Xilinx ISE or Vivado software to implement the core in Xilinx FPGA's. VHDL cores are available on request for ASIC, Intel/Altera, Lattice and Microsemi/Actel designs.

Table 1 shows the performance achieved with various Xilinx parts, 30 iterations and the slowest (rate 1/5 Short SF2 VL–SNR) and fastest (rate 9/10 Normal) codes.  $T_{cp}$  is the minimum clock period over recommended operating conditions. These performance figures may change due to device utilisation and configuration.

| Xilinx Part | <b>T</b> (ma)        | <i>f<sub>d</sub></i> (Mbit/s) |       |  |  |  |  |

|-------------|----------------------|-------------------------------|-------|--|--|--|--|

| XIIInx Part | T <sub>cp</sub> (ns) | Low                           | High  |  |  |  |  |

| XC7A200T-1  | 8.805                | 19.3                          | 101.9 |  |  |  |  |

| XC7A200T-2  | 7.265                | 23.4                          | 123.6 |  |  |  |  |

| XC7A200T-3  | 6.407                | 26.5                          | 140.1 |  |  |  |  |

| XC7Z030-1   | 7.873                | 21.6                          | 114.0 |  |  |  |  |

| XC7Z030-2   | 6.385                | 26.6                          | 140.6 |  |  |  |  |

| XC7Z030-3   | 6.139                | 27.7                          | 146.2 |  |  |  |  |

| XC7K160T-1  | 6.613                | 25.7                          | 135.7 |  |  |  |  |

| XC7K160T-2  | 5.512                | 30.8                          | 162.9 |  |  |  |  |

| XC7K160T-3  | 5.005                | 33.9                          | 179.4 |  |  |  |  |

| XCKU035-1   | 5.271                | 32.2                          | 170.3 |  |  |  |  |

| XCKU035-2   | 4.489                | 37.9                          | 200.0 |  |  |  |  |

| XCKU035-3   | 3.915                | 43.4                          | 229.3 |  |  |  |  |

| XCKU3P-1    | 3.869                | 43.9                          | 232.0 |  |  |  |  |

| XCKU3P-2    | 3.382                | 50.3                          | 265.5 |  |  |  |  |

| XCKU3P-3    | 3.092                | 55.0                          | 290.4 |  |  |  |  |

Table 1: Performance of Xilinx parts.

# **Signal Descriptions**

| Oigile |                                      |

|--------|--------------------------------------|

| BDF    | BCH Decoder Fail                     |

| BED    | BCH Error Location Polynomial Degree |

| CHK    | Parity Check                         |

| CLK    | System Clock                         |

| DS     | Descrambler Select                   |

|        | 0 = No descrambling                  |

|        | 1 = Descrambling enabled             |

| FULL   | Decoder Full (new data not accepted) |

|        |                                      |

<sup>1</sup> December 2021 (Version 1.04)

| M     | Early Stopping Mode                             |

|-------|-------------------------------------------------|

|       | 0 = No early stopping                           |

|       | 1 = Early stopping enabled                      |

| NI    | Number of Iterations minus one (0–255)          |

|       | I = NI+1 where <i>I</i> is number of iterations |

| PLS   | Physical Layer Signalling Select (2–124)        |

|       | $(b_0 b_1 b_2 b_3 b_4 b_5 b_6)$ . See Table 3   |

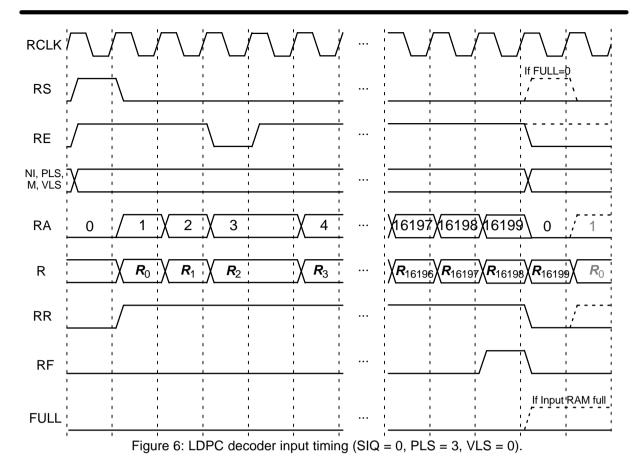

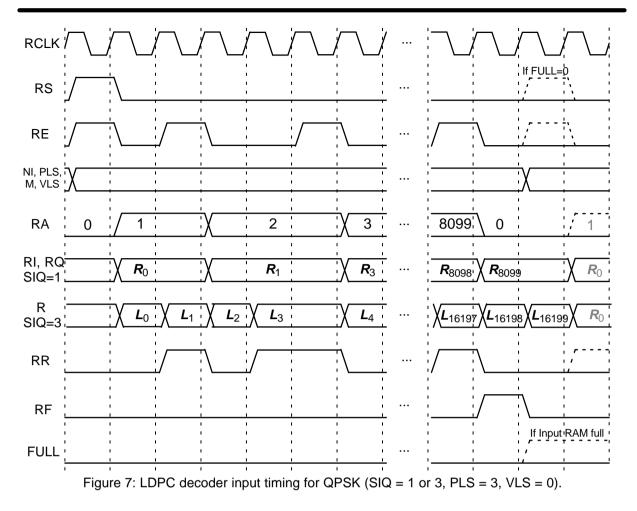

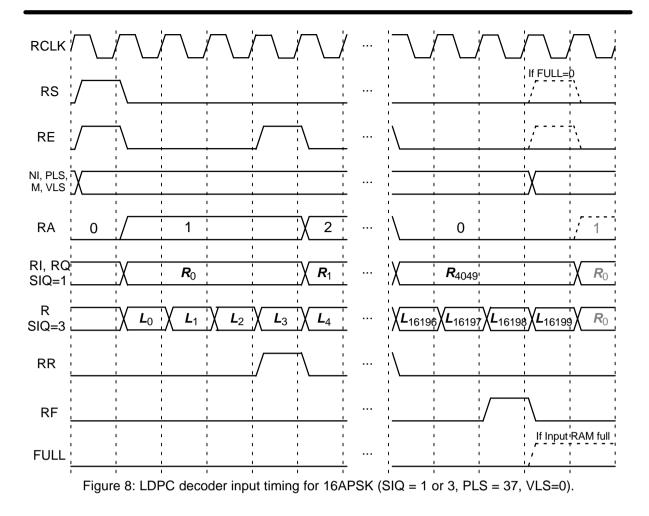

| R     | Received LLR Data (8-bit)                       |

| RA    | Received Data Address                           |

| RCLK  | Received Data Clock                             |

| RE    | Received Data Enable                            |

| RF    | Received Data Finish                            |

| RI    | Received Inphase Data (11-bit)                  |

| RQ    | Received Quadrature Data (11-bit)               |

| RR    | Received Data Ready                             |

| RS    | Received Data Start                             |

| RST   | Synchronous Reset                               |

| RSYNC | RCLK and CLK equal                              |

| S     | Symbol Value (11–bit)                           |

| SA    | Symbol Address                                  |

| SIQ   | Inphase and Quadrature Select                   |

|       | 0 = No Demapping (deinterleaved data            |

|       | input to R)                                     |

|       | 1 = Demapping (data input to RI and RQ)         |

|       | 3 = No Demapping (interleaved data              |

|       | input to R)                                     |

| SM    | Symbol Memory Select                            |

|       | 0 = ROM                                         |

|       | 1 = RAM                                         |

| SR    | Symbol Ready                                    |

| SS    | Symbol Start                                    |

| VLS   | Very Low SNR (VL–SNR) Select (0–8)              |

|       | See Table 3                                     |

| XCLK  | Decoded Data Clock                              |

| XD    | Decoded Data (2-bit)                            |

| XDA   | Decoded Data Address                            |

| XDR   | Decoded Data Ready                              |

| XSYNC | XCLK and CLK equal                              |

|       |                                                 |

Table 3 lists the 116 different modulation and coding combinations selected by PLS and VLS. The information data length is given by *K* and the number of two dimensional modulated symbols is given by  $N_s$ .  $R_{\text{eff}} = K/N_s$  is the bandwidth efficiency in bit/sym (synchronisation, PLS and VL–SNR symbols not included).  $E_b/N_0$  is the energy per bit to single sided noise density ratio for an additive white Gaussian noise (AWGN) channel at a bit error rate (BER) of  $10^{-5}$ .  $E_s/N_0$  is the energy per two dimensional symbol to single sided noise density ratio for an AWGN channel at a frame error rate (FER) of  $10^{-3}$ . *A* is the no–noise average signal amplitude value which the input must be scaled to when demapping is used. SS, SC and SI

are selection parameters used to select the signal set, LDPC code and symbol interleaver, respectively. The value SH is the number of bits that the squared Euclidean distance of a received point is shifted to the right. This value is then divided by 2 and rounded to the nearest integer. MS is the check message scale factor used by the LDPC decoder.

Table 4 lists the 60 different LDPC codes selected by SC. The coded data length after rate matching is given by *N*. The BCH error correction capability is given by *t*. The number of circulant rows is given by *q*. The minimum, maximum and average check degree values are given by  $d_{c,min}$ ,  $d_{c,max}$  and  $d_c$ , respectively. The frequency of each check degree value from  $d_{c,min}$  to  $d_{c,max}$  is given by  $d_{c,freq}$ . The parameter  $qd_c$  is the complexity of the LDPC code with  $f_d$  being the decoder speed when a CLK of frequency  $F_d = 100$  MHz is used.

# LDPC Decoder Parameters

For binary modulation, we model the received sample at time *i* as

$$r_i = A(s_i + n_i) \tag{1}$$

where *A* is the no–noise amplitude,  $s_i$  is the modulated signal with value +1 for coded bit  $y_i = 0$  and -1 for  $y_i = 1$ ,  $n_i$  is white Gaussian noise with normalised variance

$$\sigma^2 = 1/(2RE_b/N_0) \tag{2}$$

and R = K/N is the code rate.

The value of *A* directly corresponds to the 8–bit two's complement inputs for R (shown in Table 2). The 8–bit inputs have 256 quantisation regions. The quantisation regions are labelled from –128 to 127. For example, one could have A = 15.7. This value of *A* lies in quantisation region 16 (which has a range between 15.5 and 16.5).

| Decimal | Binary   | Range         |  |  |  |  |

|---------|----------|---------------|--|--|--|--|

| 127     | 01111111 | 126.5⇔∞       |  |  |  |  |

| 126     | 01111110 | 125.5⇔126.5   |  |  |  |  |

| :       | :        | :             |  |  |  |  |

| 2       | 00000010 | 1.5⇔2.5       |  |  |  |  |

| 1       | 00000001 | 0.5⇔1.5       |  |  |  |  |

| 0       | 0000000  | –0.5⇔0.5      |  |  |  |  |

| -1      | 11111111 | –1.5↔–0.5     |  |  |  |  |

| -2      | 11111110 | –2.5⇔–1.5     |  |  |  |  |

| :       | :        | :             |  |  |  |  |

| -127    | 10000001 | –127.5↔–126.5 |  |  |  |  |

| -128    | 1000000  | –∞⇔–127.5     |  |  |  |  |

## Table 3: MODCOD Coding

| PLS | MODCOD Name       | к     | Ns    | R <sub>eff</sub> (bit/<br>sym) | <i>E<sub>b</sub>/N</i> 0<br>(dB) | <i>E<sub>s</sub>/N</i> 0<br>(dB) | А    | SS | sc | SI | SH | MS   |

|-----|-------------------|-------|-------|--------------------------------|----------------------------------|----------------------------------|------|----|----|----|----|------|

| 2   | QPSK 1/4 Normal   | 16008 | 32400 | 0.49407                        | 0.53                             | -2.47                            | 239  | 0  | 10 | -1 | 0  | 0.97 |

| 3   | QPSK 1/4 Short    | 3072  | 8100  | 0.37926                        | 0.80                             | -3.42                            | 173  | 0  | 0  | -1 | 0  | 0.97 |

| 4   | QPSK 1/3 Normal   | 21408 | 32400 | 0.66074                        | 0.51                             | -1.26                            | 264  | 0  | 11 | -1 | 0  | 0.97 |

| 5   | QPSK 1/3 Short    | 5232  | 8100  | 0.64593                        | 0.76                             | -1.14                            | 230  | 0  | 1  | -1 | 0  | 0.97 |

| 6   | QPSK 2/5 Normal   | 25728 | 32400 | 0.79407                        | 0.67                             | -0.31                            | 218  | 0  | 12 | -1 | 0  | 0.97 |

| 7   | QPSK 2/5 Short    | 6312  | 8100  | 0.77926                        | 0.93                             | -0.18                            | 214  | 0  | 2  | -1 | 0  | 0.97 |

| 8   | QPSK 1/2 Normal   | 32208 | 32400 | 0.99407                        | 1.05                             | 1.03                             | 266  | 0  | 13 | -1 | 0  | 0.95 |

| 9   | QPSK 1/2 Short    | 7032  | 8100  | 0.86815                        | 1.18                             | 0.56                             | 350  | 0  | 3  | -1 | 0  | 0.96 |

| 10  | QPSK 3/5 Normal   | 38688 | 32400 | 1.19407                        | 1.51                             | 2.28                             | 397  | 0  | 14 | -1 | 0  | 0.79 |

| 11  | QPSK 3/5 Short    | 9552  | 8100  | 1.17926                        | 1.74                             | 2.42                             | 396  | 0  | 4  | -1 | 0  | 0.79 |

| 12  | QPSK 2/3 Normal   | 43040 | 32400 | 1.32840                        | 1.81                             | 3.06                             | 760  | 0  | 15 | -1 | 0  | 0.91 |

| 13  | QPSK 2/3 Short    | 10632 | 8100  | 1.31259                        | 2.05                             | 3.20                             | 743  | 0  | 5  | -1 | 0  | 0.91 |

| 14  | QPSK 3/4 Normal   | 48408 | 32400 | 1.49407                        | 2.26                             | 4.02                             | 912  | 0  | 16 | -1 | 0  | 0.88 |

| 15  | QPSK 3/4 Short    | 11712 | 8100  | 1.44593                        | 2.53                             | 4.14                             | 866  | 0  | 6  | -1 | 0  | 0.90 |

| 16  | QPSK 4/5 Normal   | 51648 | 32400 | 1.59407                        | 2.61                             | 4.65                             | 1018 | 0  | 17 | -1 | 0  | 0.86 |

| 17  | QPSK 4/5 Short    | 12432 | 8100  | 1.53481                        | 2.87                             | 4.73                             | 1017 | 0  | 7  | -1 | 0  | 0.90 |

| 18  | QPSK 5/6 Normal   | 53840 | 32400 | 1.66173                        | 2.92                             | 5.14                             | 1059 | 0  | 18 | -1 | 0  | 0.87 |

| 19  | QPSK 5/6 Short    | 13152 | 8100  | 1.62370                        | 3.17                             | 5.28                             | 1014 | 0  | 8  | -1 | 0  | 0.88 |

| 20  | QPSK 8/9 Normal   | 57472 | 32400 | 1.77383                        | 3.66                             | 6.17                             | 1226 | 0  | 19 | -1 | 0  | 0.87 |

| 21  | QPSK 8/9 Short    | 14232 | 8100  | 1.75704                        | 3.87                             | 6.33                             | 1142 | 0  | 9  | -1 | 0  | 0.88 |

| 22  | QPSK 9/10 Normal  | 58192 | 32400 | 1.79605                        | 3.82                             | 6.38                             | 1328 | 0  | 20 | -1 | 0  | 0.87 |

| 24  | 8PSK 3/5 Normal   | 38688 | 21600 | 1.79111                        | 3.04                             | 5.59                             | 374  | 1  | 14 | 3  | 11 | 0.97 |

| 25  | 8PSK 3/5 Short    | 9552  | 5400  | 1.76889                        | 3.28                             | 5.73                             | 264  | 1  | 4  | 3  | 10 | 0.94 |

| 26  | 8PSK 2/3 Normal   | 43040 | 21600 | 1.99259                        | 3.56                             | 6.56                             | 310  | 1  | 15 | 0  | 10 | 0.95 |

| 27  | 8PSK 2/3 Short    | 10632 | 5400  | 1.96889                        | 3.77                             | 6.71                             | 580  | 1  | 5  | 0  | 11 | 0.85 |

| 28  | 8PSK 3/4 Normal   | 48408 | 21600 | 2.24111                        | 4.37                             | 7.88                             | 645  | 1  | 16 | 0  | 11 | 0.83 |

| 29  | 8PSK 3/4 Short    | 11712 | 5400  | 2.16889                        | 4.67                             | 8.02                             | 346  | 1  | 6  | 0  | 9  | 0.88 |

| 30  | 8PSK 5/6 Normal   | 53840 | 21600 | 2.49259                        | 5.32                             | 9.30                             | 555  | 1  | 18 | 0  | 10 | 0.79 |

| 31  | 8PSK 5/6 Short    | 13152 | 5400  | 2.43556                        | 5.68                             | 9.50                             | 207  | 1  | 8  | 0  | 7  | 0.87 |

| 32  | 8PSK 8/9 Normal   | 57472 | 21600 | 2.66074                        | 6.36                             | 10.62                            | 466  | 1  | 19 | 0  | 9  | 0.84 |

| 33  | 8PSK 8/9 Short    | 14232 | 5400  | 2.63556                        | 6.58                             | 10.79                            | 482  | 1  | 9  | 0  | 9  | 0.84 |

| 34  | 8PSK 9/10 Normal  | 58192 | 21600 | 2.69407                        | 6.57                             | 10.89                            | 345  | 1  | 20 | 0  | 8  | 0.84 |

| 36  | 16APSK 2/3 Normal | 43040 | 16200 | 2.65679                        | 4.70                             | 8.96                             | 353  | 2  | 15 | 0  | 9  | 0.90 |

| 37  | 16APSK 2/3 Short  | 10632 | 4050  | 2.62519                        | 4.93                             | 9.11                             | 540  | 2  | 5  | 0  | 10 | 0.87 |

| 38  | 16APSK 3/4 Normal | 48408 | 16200 | 2.98815                        | 5.44                             | 10.20                            | 617  | 3  | 16 | 0  | 10 | 0.85 |

| 39  | 16APSK 3/4 Short  | 11712 | 4050  | 2.89185                        | 5.73                             | 10.34                            | 321  | 3  | 6  | 0  | 8  | 0.88 |

| 40  | 16APSK 4/5 Normal | 51648 | 16200 | 3.18815                        | 5.96                             | 11.00                            | 485  | 4  | 17 | 0  | 9  | 0.83 |

| 41  | 16APSK 4/5 Short  | 12432 | 4050  | 3.06963                        | 6.22                             | 11.09                            | 490  | 4  | 7  | 0  | 9  | 0.87 |

| 42  | 16APSK 5/6 Normal | 53840 | 16200 | 3.32346                        | 6.33                             | 11.56                            | 369  | 5  | 18 | 0  | 8  | 0.83 |

| 43  | 16APSK 5/6 Short  | 13152 | 4050  | 3.24741                        | 6.64                             | 11.75                            | 176  | 5  | 8  | 0  | 6  | 0.87 |

| 44  | 16APSK 8/9 Normal | 57472 | 16200 | 3.54765                        | 7.31                             | 12.82                            | 297  | 6  | 19 | 0  | 7  | 0.85 |

1 December 2021 (Version 1.04)

## Table 3: MODCOD Coding (cont.)

| PLS/<br>VLS | MODCOD Name          | к     | Ns    | R <sub>eff</sub> (bit/<br>sym) | <i>Е<sub>b</sub>/N</i> 0<br>(dB) | <i>E<sub>s</sub>/N</i> 0<br>(dB) | А   | SS | sc | SI | SH | MS   |

|-------------|----------------------|-------|-------|--------------------------------|----------------------------------|----------------------------------|-----|----|----|----|----|------|

| 45          | 16APSK 8/9 Short     | 14232 | 4050  | 3.51407                        | 7.53                             | 13.00                            | 421 | 6  | 9  | 0  | 8  | 0.84 |

| 46          | 16APSK 9/10 Normal   | 58192 | 16200 | 3.59210                        | 7.49                             | 13.05                            | 435 | 7  | 20 | 0  | 8  | 0.85 |

| 48          | 32APSK 3/4 Normal    | 48408 | 12960 | 3.73419                        | 7.05                             | 12.78                            | 402 | 8  | 16 | 0  | 9  | 0.94 |

| 49          | 32APSK 3/4 Short     | 11712 | 3240  | 3.61481                        | 7.43                             | 13.01                            | 584 | 8  | 6  | 0  | 9  | 0.90 |

| 50          | 32APSK 4/5 Normal    | 51648 | 12960 | 3.98519                        | 7.67                             | 13.67                            | 583 | 9  | 17 | 0  | 10 | 0.94 |

| 51          | 32APSK 4/5 Short     | 12432 | 3240  | 3.83704                        | 7.98                             | 13.83                            | 456 | 9  | 7  | 0  | 8  | 0.90 |

| 52          | 32APSK 5/6 Normal    | 53840 | 12960 | 4.15432                        | 8.05                             | 14.24                            | 453 | 10 | 18 | 0  | 9  | 0.92 |

| 53          | 32APSK 5/6 Short     | 13152 | 3240  | 4.05926                        | 8.40                             | 14.46                            | 485 | 10 | 8  | 0  | 8  | 0.88 |

| 54          | 32APSK 8/9 Normal    | 57472 | 12960 | 4.43457                        | 9.08                             | 15.56                            | 583 | 11 | 19 | 0  | 8  | 0.85 |

| 55          | 32APSK 8/9 Short     | 14232 | 3240  | 4.39259                        | 9.31                             | 15.75                            | 533 | 11 | 9  | 0  | 8  | 0.85 |

| 56          | 32APSK 9/10 Normal   | 58192 | 12960 | 4.49012                        | 9.30                             | 15.84                            | 424 | 12 | 20 | 0  | 7  | 0.84 |

| 64/0        | QPSK 2/9 Normal      | 14208 | 30780 | 0.46160                        | 0.49                             | -2.81                            | 191 | 0  | 36 | -1 | 0  | 0.97 |

| 64/1        | BPSK 1/5 Medium      | 5660  | 30780 | 0.18389                        | 0.71                             | -6.57                            | 192 | -1 | 33 | -1 | 0  | 0.97 |

| 64/2        | BPSK 11/45 Medium    | 7740  | 30780 | 0.25146                        | 0.58                             | -5.40                            | 207 | -1 | 34 | -1 | 0  | 0.97 |

| 64/3        | BPSK 1/3 Medium      | 10620 | 30780 | 0.34503                        | 0.68                             | -3.91                            | 280 | -1 | 35 | -1 | 0  | 0.97 |

| 64/4        | BPSK–S 1/5 Short     | 2512  | 30780 | 0.08161                        | 1.21                             | -9.66                            | 196 | -2 | 21 | -1 | 0  | 0.97 |

| 64/7        | BPSK–S 11/45 Short   | 3792  | 30780 | 0.12320                        | 0.79                             | -8.31                            | 201 | -2 | 22 | -1 | 0  | 0.97 |

| 65/5        | BPSK 4/15 Short      | 4152  | 14976 | 0.27724                        | 0.88                             | -4.74                            | 169 | -1 | 24 | -1 | 0  | 0.96 |

| 65/6        | BPSK 1/5 Short       | 3072  | 14976 | 0.20513                        | 0.86                             | -6.03                            | 189 | -1 | 23 | -1 | 0  | 0.97 |

| 65/8        | BPSK 1/3 Short       | 5232  | 14976 | 0.34936                        | 0.88                             | -3.68                            | 259 | -1 | 25 | -1 | 0  | 0.96 |

| 66          | QPSK 13/45 Normal    | 18528 | 32400 | 0.57185                        | 0.51                             | -1.89                            | 177 | 0  | 37 | -1 | 0  | 0.97 |

| 67          | QPSK 9/20 Normal     | 28968 | 32400 | 0.89407                        | 0.81                             | 0.33                             | 233 | 0  | 38 | -1 | 0  | 0.97 |

| 68          | QPSK 11/20 Normal    | 35448 | 32400 | 1.09407                        | 1.15                             | 1.55                             | 267 | 0  | 41 | -1 | 0  | 0.95 |

| 69          | 8APSK 5/9–L Normal   | 35808 | 21600 | 1.65778                        | 2.65                             | 4.85                             | 452 | 13 | 42 | 0  | 12 | 0.95 |

| 70          | 8APSK 26/45–L Normal | 37248 | 21600 | 1.72444                        | 2.92                             | 5.27                             | 429 | 14 | 43 | 0  | 12 | 0.95 |

| 71          | 8PSK 23/36 Normal    | 41208 | 21600 | 1.90778                        | 3.42                             | 6.22                             | 243 | 1  | 47 | 0  | 9  | 0.79 |

| 72          | 8PSK 25/36 Normal    | 44808 | 21600 | 2.07444                        | 3.92                             | 7.08                             | 432 | 1  | 51 | 2  | 11 | 0.93 |

| 73          | 8PSK 13/18 Normal    | 46608 | 21600 | 2.15778                        | 4.17                             | 7.51                             | 604 | 1  | 53 | 2  | 11 | 0.83 |

| 74          | 16APSK 1/2–L Normal  | 32208 | 16200 | 1.98815                        | 3.12                             | 6.12                             | 296 | 21 | 39 | 10 | 10 | 0.95 |

| 75          | 16APSK 8/15-L Normal | 34368 | 16200 | 2.12148                        | 3.50                             | 6.75                             | 270 | 21 | 40 | 6  | 10 | 0.94 |

| 76          | 16APSK 5/9–L Normal  | 35808 | 16200 | 2.21037                        | 3.52                             | 6.97                             | 425 | 21 | 42 | 5  | 11 | 0.97 |

| 77          | 16APSK 26/45 Normal  | 37248 | 16200 | 2.29926                        | 3.90                             | 7.54                             | 504 | 15 | 44 | 9  | 11 | 0.96 |

| 78          | 16APSK 3/5 Normal    | 38688 | 16200 | 2.38815                        | 4.18                             | 7.96                             | 219 | 15 | 14 | 10 | 9  | 0.95 |

| 79          | 16APSK 3/5–L Normal  | 38688 | 16200 | 2.38815                        | 3.73                             | 7.53                             | 175 | 22 | 45 | 0  | 8  | 0.97 |

| 80          | 16APSK 28/45 Normal  | 40128 | 16200 | 2.47704                        | 4.28                             | 8.22                             | 342 | 16 | 46 | 7  | 10 | 0.91 |

| 81          | 16APSK 23/36 Normal  | 41208 | 16200 | 2.54370                        | 4.37                             | 8.44                             | 264 | 17 | 47 | 8  | 9  | 0.95 |

| 82          | 16APSK 2/3–L Normal  | 43008 | 16200 | 2.65481                        | 4.26                             | 8.52                             | 189 | 23 | 49 | 0  | 8  | 0.95 |

| 83          | 16APSK 25/36 Normal  | 44808 | 16200 | 2.76593                        | 4.88                             | 9.31                             | 397 | 17 | 51 | 6  | 10 | 0.96 |

| 84          | 16APSK 13/18 Normal  | 46608 | 16200 | 2.87704                        | 5.19                             | 9.77                             | 511 | 3  | 53 | 8  | 10 | 0.79 |

| 85          | 16APSK 7/9 Normal    | 50208 | 16200 | 3.09926                        | 5.79                             | 10.70                            | 535 | 18 | 57 | 10 | 10 | 0.79 |

| 86          | 16APSK 77/90 Normal  | 55248 | 16200 | 3.41037                        | 6.65                             | 11.98                            | 500 | 19 | 59 | 1  | 9  | 0.79 |

### Table 3: MODCOD Coding (cont.)

| PLS | MODCOD Name            | к     | Ns    | R <sub>eff</sub> (bit/<br>sym) | <i>Е<sub>b</sub>/N</i> 0<br>(dB) | <i>E<sub>s</sub>/N</i> 0<br>(dB) | А   | SS | sc | SI | ѕн | MS   |

|-----|------------------------|-------|-------|--------------------------------|----------------------------------|----------------------------------|-----|----|----|----|----|------|

| 87  | 32APSK 2/3–L Normal    | 43040 | 12960 | 3.32099                        | 6.00                             | 11.21                            | 354 | 24 | 15 | 12 | 9  | 0.96 |

| 89  | 32APSK 32/45 Normal    | 45888 | 12960 | 3.54074                        | 6.40                             | 11.89                            | 699 | 27 | 52 | 14 | 11 | 0.94 |

| 90  | 32APSK 11/15 Normal    | 47328 | 12960 | 3.65185                        | 6.68                             | 12.30                            | 364 | 28 | 54 | 14 | 9  | 0.95 |

| 91  | 32APSK 7/9 Normal      | 50208 | 12960 | 3.87407                        | 7.30                             | 13.17                            | 528 | 29 | 57 | 13 | 10 | 0.83 |

| 92  | 64APSK 32/45–L Normal  | 45888 | 10800 | 4.24889                        | 7.81                             | 14.09                            | 169 | 30 | 52 | 18 | 6  | 0.94 |

| 93  | 64APSK 11/15 Normal    | 47328 | 10800 | 4.38222                        | 8.52                             | 14.93                            | 499 | 33 | 54 | 25 | 9  | 0.95 |

| 95  | 64APSK 7/9 Normal      | 50208 | 10800 | 4.64889                        | 8.84                             | 15.52                            | 414 | 31 | 58 | 17 | 8  | 0.95 |

| 97  | 64APSK 4/5 Normal      | 51648 | 10800 | 4.78222                        | 9.16                             | 15.95                            | 540 | 31 | 17 | 16 | 9  | 0.92 |

| 99  | 64APSK 5/6 Normal      | 53840 | 10800 | 4.98519                        | 9.61                             | 16.59                            | 303 | 32 | 18 | 21 | 7  | 0.93 |

| 100 | 128APSK 3/4 Normal     | 48408 | 9258  | 5.22878                        | 10.68                            | 17.87                            | 507 | 34 | 56 | 22 | 8  | 0.95 |

| 101 | 128APSK 7/9 Normal     | 50208 | 9258  | 5.42320                        | 11.34                            | 18.67                            | 698 | 35 | 57 | 20 | 9  | 0.91 |

| 102 | 256APSK 29/45–L Normal | 41568 | 8100  | 5.13185                        | 9.98                             | 17.09                            | 540 | 36 | 48 | 19 | 8  | 0.97 |

| 103 | 256APSK 2/3–L Normal   | 43008 | 8100  | 5.30963                        | 10.25                            | 17.51                            | 510 | 39 | 49 | 0  | 8  | 0.97 |

| 104 | 256APSK 31/45–L Normal | 44448 | 8100  | 5.48741                        | 10.87                            | 18.25                            | 546 | 36 | 50 | 23 | 8  | 0.94 |

| 105 | 256APSK 32/45 Normal   | 45888 | 8100  | 5.66519                        | 11.27                            | 18.79                            | 561 | 37 | 52 | 26 | 8  | 0.93 |

| 106 | 256APSK 11/45–L Normal | 47328 | 8100  | 5.84296                        | 11.28                            | 18.95                            | 446 | 40 | 55 | 0  | 7  | 0.97 |

| 107 | 256APSK 3/4 Normal     | 48408 | 8100  | 5.97630                        | 11.93                            | 19.69                            | 481 | 38 | 56 | 24 | 7  | 0.95 |

| 108 | QPSK 11/45 Short       | 3792  | 8100  | 0.46815                        | 0.74                             | -2.57                            | 180 | 0  | 26 | -1 | 0  | 0.97 |

| 109 | QPSK 4/15 Short        | 4152  | 8100  | 0.51259                        | 0.80                             | -2.14                            | 151 | 0  | 27 | -1 | 0  | 0.97 |

| 110 | QPSK 14/45 Short       | 4872  | 8100  | 0.60148                        | 0.78                             | -1.44                            | 186 | 0  | 28 | -1 | 0  | 0.97 |

| 111 | QPSK 7/15 Short        | 7392  | 8100  | 0.91259                        | 1.20                             | 0.75                             | 198 | 0  | 29 | -1 | 0  | 0.95 |

| 112 | QPSK 8/15 Short        | 8472  | 8100  | 1.04593                        | 1.44                             | 1.59                             | 212 | 0  | 30 | -1 | 0  | 0.95 |

| 113 | QPSK 32/45 Short       | 11352 | 8100  | 1.40148                        | 2.13                             | 3.59                             | 613 | 0  | 32 | -1 | 0  | 0.87 |

| 114 | 8PSK 7/15 Short        | 7392  | 5400  | 1.36889                        | 2.44                             | 3.79                             | 242 | 1  | 29 | 2  | 10 | 0.96 |

| 115 | 8PSK 8/15 Short        | 8472  | 5400  | 1.56889                        | 2.85                             | 4.76                             | 338 | 1  | 30 | 2  | 11 | 0.97 |

| 116 | 8PSK 26/45 Short       | 9192  | 5400  | 1.70222                        | 3.12                             | 5.42                             | 384 | 1  | 31 | 2  | 11 | 0.97 |

| 117 | 8PSK 32/45 Short       | 11352 | 5400  | 2.10222                        | 4.32                             | 7.51                             | 275 | 1  | 32 | 0  | 9  | 0.77 |

| 118 | 16APSK 7/15 Short      | 7392  | 4050  | 1.82519                        | 3.46                             | 6.03                             | 155 | 20 | 29 | 3  | 8  | 0.96 |

| 119 | 16APSK 8/15 Short      | 8472  | 4050  | 2.09185                        | 3.88                             | 7.04                             | 211 | 16 | 30 | 3  | 9  | 0.94 |

| 120 | 16APSK 26/45 Short     | 9192  | 4050  | 2.26963                        | 4.16                             | 7.70                             | 445 | 15 | 31 | 4  | 11 | 0.94 |

| 121 | 16APSK 3/5 Short       | 9552  | 4050  | 2.35852                        | 4.44                             | 8.13                             | 219 | 15 | 4  | 9  | 9  | 0.93 |

| 122 | 16APSK 32/45 Short     | 11352 | 4050  | 2.80296                        | 5.33                             | 9.78                             | 532 | 3  | 32 | 0  | 11 | 0.92 |

| 123 | 32APSK 2/3 Short       | 10632 | 3240  | 3.28148                        | 6.24                             | 11.37                            | 361 | 25 | 5  | 15 | 9  | 0.92 |

| 124 | 32APSK 32/45 Short     | 11352 | 3240  | 3.50370                        | 6.72                             | 12.13                            | 503 | 26 | 32 | 11 | 10 | 0.92 |

Due to quantisation and limiting effects the value of *A* should be adjusted according to the received signal to noise ratio. Where QPSK modulation is used in Table 3, the value of A should be divided by  $32\sqrt{2}$ . For example, for PLS = 2, *A* = 239 when using RI and RQ. Dividing by  $32\sqrt{2}$  gives *A* = 5.3 when data is input to R.

### Demapping

For 90° binary shift keying ( $\pi/2$  BPSK), quadrature phase shift keying (QPSK), eight phase shift keying (8PSK) and amplitude phase shift keying (APSK) the two–dimensional (2–D) received signal is modelled by the inphase  $r_j^1$  and quadrature  $r_j^{Q}$  received values at symbol index *j*

# Table 4: Decoder Speeds, $F_d = 100 \text{ MHz}$

| sc | LDPC Code ID        | к     | N     | t  | q   | d <sub>c, min</sub> | d <sub>c, max</sub> | d <sub>c,freq</sub> | d <sub>c</sub> | qd <sub>c</sub> | <sup>f</sup> d<br>(Mbit/s) |

|----|---------------------|-------|-------|----|-----|---------------------|---------------------|---------------------|----------------|-----------------|----------------------------|

| 0  | 1/4 Short           | 3072  | 16200 | 12 | 36  | 3                   | 4                   | (1,3)/4             | 3.75           | 135             | 18.96                      |

| 1  | 1/3 Short           | 5232  | 16200 | 12 | 30  | 5                   | 5                   | (1)                 | 5              | 150             | 29.06                      |

| 2  | 2/5 Short           | 6312  | 16200 | 12 | 27  | 6                   | 6                   | (1)                 | 6              | 162             | 32.46                      |

| 3  | 1/2 Short           | 7032  | 16200 | 12 | 25  | 4                   | 7                   | (4,9,10,2)/25       | 5.4            | 135             | 43.40                      |

| 4  | 3/5 Short           | 9552  | 16200 | 12 | 18  | 11                  | 11                  | (1)                 | 11             | 198             | 40.20                      |

| 5  | 2/3 Short           | 10632 | 16200 | 12 | 15  | 10                  | 10                  | (1)                 | 10             | 150             | 59.05                      |

| 6  | 3/4 Short           | 11712 | 16200 | 12 | 12  | 9                   | 13                  | (1,3,4,3,1)/12      | 11             | 132             | 73.92                      |

| 7  | 4/5 Short           | 12432 | 16200 | 12 | 10  | 11                  | 13                  | (1,3,6)/10          | 12.5           | 125             | 82.86                      |

| 8  | 5/6 Short           | 13152 | 16200 | 12 | 8   | 16                  | 19                  | (4,1,1,2)/8         | 17.125         | 137             | 79.98                      |

| 9  | 8/9 Short           | 14232 | 16200 | 12 | 5   | 27                  | 27                  | (1)                 | 27             | 135             | 87.83                      |

| 10 | 1/4 Normal          | 16008 | 64800 | 12 | 135 | 4                   | 4                   | (1)                 | 4              | 540             | 24.70                      |

| 11 | 1/3 Normal          | 21408 | 64800 | 12 | 120 | 5                   | 5                   | (1)                 | 5              | 600             | 29.73                      |

| 12 | 2/5 Normal          | 25728 | 64800 | 12 | 108 | 6                   | 6                   | (1)                 | 6              | 648             | 33.08                      |

| 13 | 1/2 Normal          | 32208 | 64800 | 12 | 90  | 7                   | 7                   | (1)                 | 7              | 630             | 42.60                      |

| 14 | 3/5 Normal          | 38688 | 64800 | 12 | 72  | 11                  | 11                  | (1)                 | 11             | 792             | 40.71                      |

| 15 | 2/3 Normal          | 43040 | 64800 | 10 | 60  | 10                  | 10                  | (1)                 | 10             | 600             | 59.77                      |

| 16 | 3/4 Normal          | 48408 | 64800 | 12 | 45  | 14                  | 14                  | (1)                 | 14             | 630             | 64.03                      |

| 17 | 4/5 Normal          | 51648 | 64800 | 12 | 36  | 18                  | 18                  | (1)                 | 18             | 648             | 66.42                      |

| 18 | 5/6 Normal          | 53840 | 64800 | 10 | 30  | 22                  | 22                  | (1)                 | 22             | 660             | 67.98                      |

| 19 | 8/9 Normal          | 57472 | 64800 | 8  | 20  | 27                  | 27                  | (1)                 | 27             | 540             | 88.69                      |

| 20 | 9/10 Normal         | 58192 | 64800 | 8  | 18  | 30                  | 30                  | (1)                 | 30             | 540             | 89.80                      |

| 21 | 1/5 Short SF2 VLS   | 2512  | 15390 | 12 | 36  | 2                   | 4                   | (4,13,19)/36        | 3.417          | 123             | 17.01                      |

| 22 | 11/45 Short SF2 VLS | 3792  | 15390 | 12 | 34  | 4                   | 4                   | (1)                 | 4              | 136             | 23.23                      |

| 23 | 1/5 Short VLS       | 3072  | 14976 | 12 | 36  | 3                   | 4                   | (1,3)/4             | 3.75           | 135             | 18.96                      |

| 24 | 4/15 Short VLS      | 4152  | 14976 | 12 | 33  | 4                   | 5                   | (1,10)/11           | 4.909          | 162             | 21.36                      |

| 25 | 1/3 Short VLS       | 5232  | 14976 | 12 | 30  | 5                   | 5                   | (1)                 | 5              | 150             | 29.06                      |

| 26 | 11/45 Short         | 3792  | 16200 | 12 | 34  | 4                   | 4                   | (1)                 | 4              | 136             | 23.23                      |

| 27 | 4/15 Short          | 4152  | 16200 | 12 | 33  | 4                   | 5                   | (1,10)/11           | 4.909          | 162             | 21.35                      |

| 28 | 14/45 Short         | 4872  | 16200 | 12 | 31  | 5                   | 5                   | (1)                 | 5              | 155             | 26.19                      |

| 29 | 7/15 Short          | 7392  | 16200 | 12 | 24  | 8                   | 9                   | (13,11)/24          | 8.458          | 203             | 30.34                      |

| 30 | 8/15 Short          | 8472  | 16200 | 12 | 21  | 9                   | 10                  | (1,20)/21           | 9.952          | 209             | 33.77                      |

| 31 | 26/45 Short         | 9192  | 16200 | 12 | 19  | 10                  | 10                  | (1)                 | 10             | 190             | 40.31                      |

| 32 | 32/45 Short         | 11352 | 16200 | 12 | 13  | 13                  | 13                  | (1)                 | 13             | 169             | 55.97                      |

| 33 | 1/5 Medium VLS      | 5660  | 30780 | 12 | 72  | 3                   | 4                   | (13,59)/72          | 3.819          | 275             | 17.15                      |

| 34 | 11/45 Medium VLS    | 7740  | 30780 | 12 | 68  | 4                   | 4                   | (1)                 | 4              | 272             | 23.71                      |

| 35 | 1/3 Medium VLS      | 10620 | 30780 | 12 | 60  | 5                   | 5                   | (1)                 | 5              | 300             | 29.50                      |

| 36 | 2/9 Normal VLS      | 14208 | 61560 | 12 | 140 | 4                   | 4                   | (1)                 | 4              | 560             | 21.14                      |

| 37 | 13/45 Normal        | 18528 | 64800 | 12 | 128 | 4                   | 5                   | (3,29)/32           | 4.906          | 628             | 24.58                      |

| 38 | 9/20 Normal         | 28968 | 64800 | 12 | 99  | 7                   | 7                   | (1)                 | 7              | 693             | 34.83                      |

| 39 | 90/180 Normal       | 32208 | 64800 | 12 | 90  | 7                   | 8                   | (1,8)/9             | 7.889          | 710             | 37.80                      |

| 40 | 96/180 Normal       | 34368 | 64800 | 12 | 84  | 8                   | 9                   | (5,23)/28           | 8.821          | 741             | 38.65                      |

| Table 4: Decoder | Speeds, | <i>F<sub>d</sub></i> = 100 | MHz (cont.) |

|------------------|---------|----------------------------|-------------|

|------------------|---------|----------------------------|-------------|

| sc | LDPC Code ID   | к     | N     | t  | q  | d <sub>c, min</sub> | d <sub>c,max</sub> | d <sub>c,freq</sub> | d <sub>c</sub> | qd <sub>c</sub> | <sup>f</sup> d<br>(Mbit/s) |

|----|----------------|-------|-------|----|----|---------------------|--------------------|---------------------|----------------|-----------------|----------------------------|

| 41 | 11/20 Normal   | 35448 | 64800 | 12 | 81 | 9                   | 9                  | (1)                 | 9              | 729             | 40.52                      |

| 42 | 100/180 Normal | 35808 | 64800 | 12 | 80 | 8                   | 9                  | (1,7)/8             | 8.875          | 710             | 42.03                      |

| 43 | 104/180 Normal | 37248 | 64800 | 12 | 76 | 9                   | 10                 | (3,35)/38           | 9.921          | 754             | 41.17                      |

| 44 | 26/45 Normal   | 37248 | 64800 | 12 | 76 | 10                  | 10                 | (1)                 | 10             | 760             | 40.84                      |

| 45 | 18/30 Normal   | 38688 | 64800 | 12 | 72 | 10                  | 11                 | (1,71)/72           | 10.986         | 791             | 40.76                      |

| 46 | 28/45 Normal   | 40128 | 64800 | 12 | 68 | 10                  | 10                 | (1)                 | 10             | 680             | 49.17                      |

| 47 | 23/36 Normal   | 41208 | 64800 | 12 | 65 | 10                  | 10                 | (1)                 | 10             | 650             | 52.83                      |

| 48 | 116/180 Normal | 41568 | 64800 | 12 | 64 | 11                  | 12                 | (17,47)/64          | 11.734         | 751             | 46.12                      |

| 49 | 20/30 Normal   | 43008 | 64800 | 12 | 60 | 13                  | 14                 | (59,1)/60           | 13.017         | 781             | 45.89                      |

| 50 | 124/180 Normal | 44448 | 64800 | 12 | 56 | 13                  | 14                 | (25,31)/56          | 13.554         | 759             | 48.80                      |

| 51 | 25/36 Normal   | 44808 | 64800 | 12 | 55 | 13                  | 13                 | (1)                 | 13             | 715             | 52.22                      |

| 52 | 128/180 Normal | 45888 | 64800 | 12 | 52 | 14                  | 15                 | (27,25)/52          | 14.481         | 753             | 50.78                      |

| 53 | 13/18 Normal   | 46608 | 64800 | 12 | 50 | 14                  | 14                 | (1)                 | 14             | 700             | 55.48                      |

| 54 | 132/180 Normal | 47328 | 64800 | 12 | 48 | 15                  | 16                 | (11,37)/48          | 15.771         | 757             | 52.10                      |

| 55 | 22/30 Normal   | 47328 | 64800 | 12 | 48 | 16                  | 17                 | (41,7)/48           | 16.146         | 775             | 50.89                      |

| 56 | 135/180 Normal | 48408 | 64800 | 12 | 45 | 16                  | 17                 | (2,1)/3             | 16.333         | 735             | 54.88                      |

| 57 | 140/180 Normal | 50208 | 64800 | 12 | 40 | 19                  | 20                 | (3,5)/8             | 19.625         | 785             | 53.30                      |

| 58 | 7/9 Normal     | 50208 | 64800 | 12 | 40 | 18                  | 18                 | (1)                 | 18             | 720             | 58.11                      |

| 59 | 154/180 Normal | 55248 | 64800 | 12 | 26 | 29                  | 30                 | (21,5)/26           | 29.192         | 759             | 60.66                      |

$$r_j^{l} = A(s_j^{l} + n_j^{l})$$

(3)

$$r_j^{\rm Q} = A(s_j^{\rm Q} + n_j^{\rm Q}) \tag{4}$$

where  $s_j^{I}$  and  $s_j^{Q}$  are the inphase and quadrature components of the transmitted signal which has an average energy of 1 and  $n_j^{I}$  and  $n_j^{Q}$  are the inphase inphase and quadrature AWGN, each with normalised variance

$$\sigma^2 = 1/(2R_{\rm eff}E_b/N_0) \tag{5}$$

where *s* is the number of bits in each 2–D signal set. Note that the number of coded symbols  $N_s = \lceil N/s \rceil$ , where *s* is the number of modulated bits per 2–D symbol, e.g., s = 0.5 for  $\pi/2$  BPSK SF2, s = 1 for  $\pi/2$  BPSK, s = 2 for QPSK, etc.

For the inphase RI and quadrature RQ sampled values, 11–bit two's complement quantisation is used. Table 5 gives the quantisation for RI and RQ.

For best performance with  $\pi/2$  BPSK and QPSK we recommend using the values of *A* given in Table 3. For all other signal sets, the value of *A* in Table 3 must be used, in order for the demapper to work correctly. These values of *A* were obtained experimentally in order to obtain the best performance.

#### Table 5: Quantisation for RI and RQ.

| Decimal | Binary       | Range           |

|---------|--------------|-----------------|

| 1023    | 01111111111  | 1022.5⇔∞        |

| 1022    | 01111111110  | 1021.5⇔1022.5   |

| :       | :            | :               |

| 2       | 0000000010   | 1.5⇔2.5         |

| 1       | 0000000001   | 0.5⇔1.5         |

| 0       | 0000000000   | –0.5⇔0.5        |

| -1      | 111111111111 | –1.5↔–0.5       |

| -2      | 11111111110  | –2.5↔–1.5       |

| :       | :            | :               |

| -1023   | 1000000001   | –1023.5↔–1022.5 |

| -1024   | 1000000000   | –∞⇔–1023.5      |

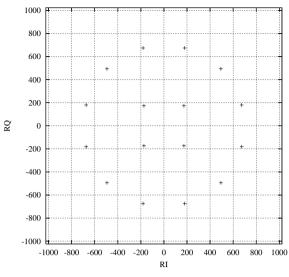

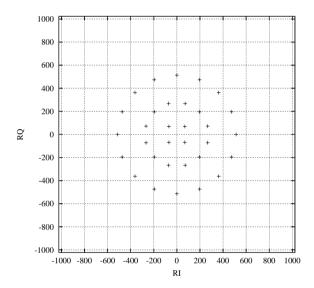

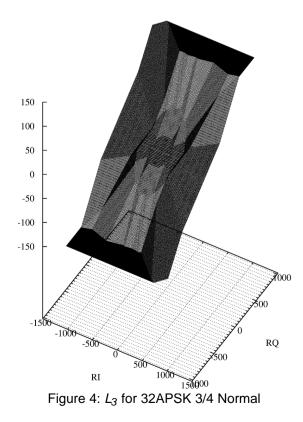

Figures 2 and 3 show the signal sets within the 11–bit quantisation regions and recommended signal amplitude for 16APSK and 32APSK, respectively, using the values of *A* for 3/4 Normal. Tables 6 and 7 gives the signal set as selected by the internal parameter SS, as given in Table 3. The parameter  $\gamma_i = R_{i+1}/R_1$  gives the ratio of the outer ring radius to the inner most ring radius. For 128APSK, the five inner rings have 16 points each, while the outer ring has 48 points. For

Figure 2: 16APSK 3/4 Normal Signal Set

Figure 3: 32APSK 3/4 Normal Signal Set

256APSK the first three signal sets have eight rings with 32 points each, while the last two signal sets have 64 rings with 4 points each. The signal set mappings and phases are given in [1,2].

To demap the received 8PSK or APSK signals into individual log–likelihood ratios (LLR) for each modulated bit, the optimum equation is

$$L_{i} = -\log\left(\frac{\sum_{h=0}^{S-1} h(i) \exp(-|s(h)-r|^{2}/c)}{\sum_{h=0}^{S-1} \overline{h(i)} \exp(-|s(h)-r|^{2}/c)}\right)$$

(6)

where *i* is the modulated bit index,  $S = 2^s$  is the number of signal points, h(i) is the *i*'th bit of *h* in binary, s(h) is the *h*'th complex signal point, *r* is the received complex value and  $c = 2A^2\sigma^2$ . By using  $\min^*(x, y) = \min(x, y) - c\ln(1 + \exp(-|x-y|/c))$  (7)

where the Jacobian logarithm is to base  $e^{1/c}$ , the LLR can be simplified to

Table 6: Signal Sets ( $\pi/2$  BPSK to 64APSK)

| Signal Set         γ <sub>1</sub> γ <sub>2</sub> γ <sub>3</sub> -2         π/2 BPSK SF2           -1         π/2 BPSK           0         QPSK           1         8PSK           2         4+12APSK           3         4+12APSK           4         412APSK           5         4+12APSK           6         4+12APSK           7         4+12APSK           8         4+12APSK           10         4+12APSK           2.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Table 6: Signal Sets ( $\pi/2$ BPSK to 64APSK) |                  |                 |  |  |  |  |  |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|------------------|-----------------|--|--|--|--|--|--|--|--|--|--|

| -1         π/2 BPSK           0         QPSK           1         8PSK           2         4+12APSK           3         4+12APSK           4         4+12APSK           5         4+12APSK           6         4+12APSK           7         4+12APSK           8         4+12APSK           9         4+12APSK           10         4+12+16APSK           11         4+12+16APSK           12         4+12+16APSK           13         2+4+2APSK           14         1+12+16APSK           15         4+12+16APSK           16         4+12+16APSK           17         4+12+16APSK           18         2+4+2APSK           19         2+4+2APSK           10         4+12+16APSK           11         4+12+16APSK           12         4+12+16APSK           13         2+4+2APSK           14         2+4+2APSK           15         4+12APSK           16         4+12APSK           17         4+12APSK           18         4+12APSK           19         2+12APSK                                                                                                                                                                                     | SS                                             | Signal Set       | <b>γ1 γ2 γ3</b> |  |  |  |  |  |  |  |  |  |  |

| 0         QPSK           1         8PSK           2         4+12APSK         3.15           3         4+12APSK         2.85           4         4+12APSK         2.75           5         4+12APSK         2.6           7         4+12APSK         2.6           7         4+12APSK         2.64           8         4+12+16APSK         2.64           9         4+12+16APSK         2.64           10         4+12+16APSK         2.64           11         4+12+16APSK         2.64           11         4+12+16APSK         2.53           12         4+12+16APSK         2.53           13         2+4+2APSK         5.32           14         2+4+2APSK         5.32           15         4+12APSK         3.7           16         4+12APSK         3.6           17         4+12APSK         3.6           18         4+12APSK         3.2           20         4+12APSK         3.2           21         8+8APSK         2.19           22         8+8APSK         2.30268           23         8+8APSK         2.85      <                                                                                                                        | -2                                             | $\pi/2$ BPSK SF2 |                 |  |  |  |  |  |  |  |  |  |  |

| 1         8PSK           2         4+12APSK         3.15           3         4+12APSK         2.85           4         4+12APSK         2.75           5         4+12APSK         2.6           7         4+12APSK         2.6           7         4+12APSK         2.6           7         4+12APSK         2.6           7         4+12APSK         2.64           9         4+12+16APSK         2.84           10         4+12+16APSK         2.64           11         4+12+16APSK         2.54           12         4+12+16APSK         2.53           13         2+4+2APSK         5.32           14         2+4+2APSK         5.32           15         4+12APSK         3.7           16         4+12APSK         3.6           17         4+12APSK         3.6           18         4+12APSK         3.2           19         4+12APSK         3.2           10         4+12APSK         3.2           12         8+8APSK         2.19           12         8+8APSK         2.30268           24         4+12+16rbAPSK         2.                                                                                                                   | -1                                             |                  |                 |  |  |  |  |  |  |  |  |  |  |

| 2         4+12APSK         3.15           3         4+12APSK         2.85           4         4+12APSK         2.75           5         4+12APSK         2.6           7         4+12APSK         2.57           8         4+12+16APSK         2.84 5.27           9         4+12+16APSK         2.64 4.64           10         4+12+16APSK         2.64 4.64           11         4+12+16APSK         2.57 4.87           10         4+12+16APSK         2.54 4.33           12         4+12+16APSK         2.53 4.30           13         2+4+2APSK         5.32 6.8           14         2+4+2APSK         5.32 6.8           14         2+4+2APSK         5.32 6.8           15         4+12APSK         3.5           17         4+12APSK         3.5           17         4+12APSK         3.6           19         4+12APSK         3.2           20         4+12APSK         3.2           21         8+8APSK         2.19           22         8+8APSK         2.30268           23         8+8APSK         2.84 5.54           26         4+12+16rbAPSK         2.8                                                                                | 0                                              | QPSK             |                 |  |  |  |  |  |  |  |  |  |  |

| 3       4+12APSK       2.85         4       4+12APSK       2.75         5       4+12APSK       2.7         6       4+12APSK       2.6         7       4+12APSK       2.57         8       4+12+16APSK       2.84 5.27         9       4+12+16APSK       2.72 4.87         10       4+12+16APSK       2.64 4.64         11       4+12+16APSK       2.53 4.30         12       4+12+16APSK       2.53 4.30         13       2+4+2APSK       6.39 8.0         14       2+4+2APSK       5.32 6.8         14       2+4+2APSK       3.7         16       4+12APSK       3.7         16       4+12APSK       3.6         17       4+12APSK       3.6         19       4+12APSK       3.2         20       4+12APSK       3.32         21       8+8APSK       2.19         22       8+8APSK       2.30268         23       8+8APSK       2.84 5.54         24       4+12+16rbAPSK       2.84 5.54         25       4+12+16rbAPSK       2.84 5.26         27       4+84+16APSK       2.6 2.99 5.6 <t< td=""><td>1</td><td>8PSK</td><td></td></t<>                                                                                                                     | 1                                              | 8PSK             |                 |  |  |  |  |  |  |  |  |  |  |

| 4       4+12APSK       2.75         5       4+12APSK       2.7         6       4+12APSK       2.6         7       4+12APSK       2.57         8       4+12+16APSK       2.84 5.27         9       4+12+16APSK       2.64 4.64         10       4+12+16APSK       2.64 4.64         11       4+12+16APSK       2.53 4.30         12       4+12+16APSK       2.53 4.30         13       2+4+2APSK       5.32 6.8         14       2+4+2APSK       6.39 8.0         15       4+12APSK       3.7         16       4+12APSK       3.5         17       4+12APSK       3.6         19       4+12APSK       3.2         20       4+12APSK       3.2         20       4+12APSK       3.32         21       8+8APSK       2.19         22       8+8APSK       2.30268         23       8+8APSK       2.84 5.54         24       4+12+16rbAPSK       2.84 5.54         25       4+12+16rbAPSK       2.84 5.26         27       4+84+16APSK       2.6 2.99 5.6         28       4+8+4+16APSK       2.6 2.99 5.6      <                                                                                                                                                  | 2                                              | 4+12APSK         | 3.15            |  |  |  |  |  |  |  |  |  |  |

| 5       4+12APSK       2.7         6       4+12APSK       2.6         7       4+12APSK       2.57         8       4+12+16APSK       2.84 5.27         9       4+12+16APSK       2.72 4.87         10       4+12+16APSK       2.64 4.64         11       4+12+16APSK       2.54 4.33         12       4+12+16APSK       2.53 4.30         13       2+4+2APSK       5.32 6.8         14       2+4+2APSK       5.32 6.8         14       2+4+2APSK       6.39 8.0         15       4+12APSK       3.7         16       4+12APSK       3.5         17       4+12APSK       3.6         19       4+12APSK       3.2         20       4+12APSK       3.2         21       8+8APSK       2.19         22       8+8APSK       2.30268         23       8+8APSK       2.84 5.54         24       4+12+16rbAPSK       2.84 5.54         25       4+12+16rbAPSK       2.84 5.54         26       4+12+16rbAPSK       2.6 2.99 5.6         25       4+12+16rbAPSK       2.6 2.99 5.6         26       4+8+4+16APSK       2.6 2.86 5.6                                                                                                                                    | 3                                              | 4+12APSK         | 2.85            |  |  |  |  |  |  |  |  |  |  |

| 6         4+12APSK         2.6           7         4+12APSK         2.57           8         4+12+16APSK         2.84 5.27           9         4+12+16APSK         2.72 4.87           10         4+12+16APSK         2.64 4.64           11         4+12+16APSK         2.53 4.30           12         4+12+16APSK         2.53 4.30           13         2+4+2APSK         5.32 6.8           14         2+4+2APSK         6.39 8.0           15         4+12APSK         3.7           16         4+12APSK         3.5           17         4+12APSK         3.6           19         4+12APSK         3.2           20         4+12APSK         3.2           21         8+8APSK         2.19           22         8+8APSK         2.30268           23         8+8APSK         2.30268           24         4+12+16rbAPSK         2.84 5.54           25         4+12+16rbAPSK         2.6 2.99 5.6           25         4+12+16rbAPSK         2.6 2.86 5.6           26         4+12+16rbAPSK         2.6 2.86 5.6           27         4+8+4+16APSK         2.8 3.08 5.6           30 <td>4</td> <td>4+12APSK</td> <td>2.75</td>                      | 4                                              | 4+12APSK         | 2.75            |  |  |  |  |  |  |  |  |  |  |

| 7       4+12APSK       2.57         8       4+12+16APSK       2.84 5.27         9       4+12+16APSK       2.72 4.87         10       4+12+16APSK       2.64 4.64         11       4+12+16APSK       2.53 4.30         12       4+12+16APSK       2.53 4.30         13       2+4+2APSK       5.32 6.8         14       2+4+2APSK       6.39 8.0         15       4+12APSK       3.7         16       4+12APSK       3.5         17       4+12APSK       3.6         19       4+12APSK       3.2         20       4+12APSK       3.2         21       8+8APSK       2.19         22       8+8APSK       2.30268         23       8+8APSK       2.30268         24       4+12+16rbAPSK       2.84 5.54         25       4+12+16rbAPSK       2.84 5.26         26       4+12+16rbAPSK       2.6 2.99 5.6         28       4+8+4+16APSK       2.6 2.86 5.6         29       4+8+4+16APSK       2.8 3.08 5.6         30       16+16+16+16APSK       1.88 2.72 3.95         31       8+16+20+20APSK       2.2 3.6 5.2         32       8+                                                                                                                           | 5                                              | 4+12APSK         | 2.7             |  |  |  |  |  |  |  |  |  |  |

| 8         4+12+16APSK         2.84 5.27           9         4+12+16APSK         2.72 4.87           10         4+12+16APSK         2.64 4.64           11         4+12+16APSK         2.53 4.33           12         4+12+16APSK         2.53 4.30           13         2+4+2APSK         5.32 6.8           14         2+4+2APSK         6.39 8.0           15         4+12APSK         3.7           16         4+12APSK         3.5           17         4+12APSK         3.6           18         4+12APSK         3.2           20         4+12APSK         3.2           21         8+8APSK         2.19           22         8+8APSK         2.30268           23         8+8APSK         2.84 5.54           24         4+12+16rbAPSK         2.84 5.54           25         4+12+16rbAPSK         2.84 5.26           24         4+12+16rbAPSK         2.6 2.99 5.6           25         4+12+16rbAPSK         2.6 2.86 5.6           26         4+8+4+16APSK         2.8 3.08 5.6           30         16+16+16+16APSK         2.8 3.08 5.6           31         8+16+20+20APSK         2.2 3.5 5.0 </td <td>6</td> <td>4+12APSK</td> <td>2.6</td> | 6                                              | 4+12APSK         | 2.6             |  |  |  |  |  |  |  |  |  |  |

| 94+12+16APSK2.72 4.87104+12+16APSK2.64 4.64114+12+16APSK2.54 4.33124+12+16APSK2.53 4.30132+4+2APSK5.32 6.8142+4+2APSK6.39 8.0154+12APSK3.7164+12APSK3.5174+12APSK3.6194+12APSK3.2204+12APSK3.32218+8APSK2.19228+8APSK2.30268244+12+16rbAPSK2.84 5.54254+12+16rbAPSK2.84 5.54264+12+16rbAPSK2.6 2.99 5.6274+8+4+16APSK2.6 2.99 5.6294+8+4+16APSK2.83 .08 5.63016+16+16+16APSK2.82 3.02 5.2318+16+20+20APSK2.2 3.5 5.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 7                                              | 4+12APSK         | 2.57            |  |  |  |  |  |  |  |  |  |  |

| 104+12+16APSK2.64 4.64114+12+16APSK2.54 4.33124+12+16APSK2.53 4.30132+4+2APSK5.32 6.8142+4+2APSK6.39 8.0154+12APSK3.7164+12APSK3.5174+12APSK3.6184+12APSK3.6194+12APSK3.2204+12APSK3.32218+8APSK2.19228+8APSK2.30268238+8APSK2.84 5.54244+12+16rbAPSK2.84 5.54254+12+16rbAPSK2.6 2.99 5.6274+8+4+16APSK2.6 2.99 5.6294+8+4+16APSK2.83 .08 5.63016+16+16+16APSK2.2 3.6 5.2318+16+20+20APSK2.2 3.5 5.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 8                                              | 4+12+16APSK      | 2.84 5.27       |  |  |  |  |  |  |  |  |  |  |

| 114+12+16APSK2.54 4.33124+12+16APSK2.53 4.30132+4+2APSK5.32 6.8142+4+2APSK6.39 8.0154+12APSK3.7164+12APSK3.5174+12APSK3.1184+12APSK3.6194+12APSK3.2204+12APSK3.32218+8APSK2.19228+8APSK2.30268238+8APSK2.30268244+12+16rbAPSK2.84 5.54254+12+16rbAPSK2.84 5.26274+8+4+16APSK2.6 2.99 5.6284+8+4+16APSK2.6 2.305 5.6294+8+4+16APSK2.83 .08 5.63016+16+16+16APSK2.2 3.6 5.2318+16+20+20APSK2.2 3.5 5.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 9                                              | 4+12+16APSK      | 2.72 4.87       |  |  |  |  |  |  |  |  |  |  |

| 124+12+16APSK2.53 4.30132+4+2APSK5.32 6.8142+4+2APSK6.39 8.0154+12APSK3.7164+12APSK3.5174+12APSK3.1184+12APSK3.6194+12APSK3.2204+12APSK3.32218+8APSK2.19228+8APSK2.42588238+8APSK2.30268244+12+16rbAPSK2.84 5.54254+12+16rbAPSK2.84 5.54264+12+16rbAPSK2.6 2.99 5.6274+8+4+16APSK2.6 2.86 5.6294+8+4+16APSK2.6 3.08 5.63016+16+16+16APSK2.2 3.6 5.2318+16+20+20APSK2.2 3.6 5.2328+16+20+20APSK2.2 3.5 5.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 10                                             | 4+12+16APSK      | 2.64 4.64       |  |  |  |  |  |  |  |  |  |  |

| 132+4+2APSK5.32 6.8142+4+2APSK6.39 8.0154+12APSK3.7164+12APSK3.5174+12APSK3.1184+12APSK3.6194+12APSK3.2204+12APSK3.32218+8APSK2.19228+8APSK2.30268244+12+16rbAPSK2.84 5.54254+12+16rbAPSK2.84 5.54264+12+16rbAPSK2.6 2.99 5.6274+8+4+16APSK2.6 2.86 5.6294+8+4+16APSK2.83 .08 5.63016+16+16+16APSK1.88 2.72 3.95318+16+20+20APSK2.2 3.5 5.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 11                                             | 4+12+16APSK      | 2.54 4.33       |  |  |  |  |  |  |  |  |  |  |

| 142+4+2APSK6.39 8.0154+12APSK3.7164+12APSK3.5174+12APSK3.1184+12APSK3.6194+12APSK3.2204+12APSK3.32218+8APSK2.19228+8APSK2.42588238+8APSK2.30268244+12+16rbAPSK2.84 5.54254+12+16rbAPSK2.84 5.54264+12+16rbAPSK2.6 2.99 5.6274+8+4+16APSK2.6 2.86 5.6294+8+4+16APSK2.8 3.08 5.63016+16+16+16APSK2.2 3.6 5.2318+16+20+20APSK2.2 3.5 5.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 12                                             | 4+12+16APSK      | 2.53 4.30       |  |  |  |  |  |  |  |  |  |  |

| 154+12APSK3.7164+12APSK3.5174+12APSK3.1184+12APSK3.6194+12APSK3.2204+12APSK3.32218+8APSK2.19228+8APSK2.42588238+8APSK2.30268244+12+16rbAPSK2.84 5.55254+12+16rbAPSK2.84 5.54264+12+16rbAPSK2.6 2.99 5.6274+8+4+16APSK2.6 2.99 5.6284+8+4+16APSK2.6 2.86 5.6294+8+4+16APSK2.8 3.08 5.63016+16+16+16APSK1.88 2.72 3.95318+16+20+20APSK2.2 3.6 5.2328+16+20+20APSK2.2 3.5 5.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 13                                             | 2+4+2APSK        | 5.32 6.8        |  |  |  |  |  |  |  |  |  |  |

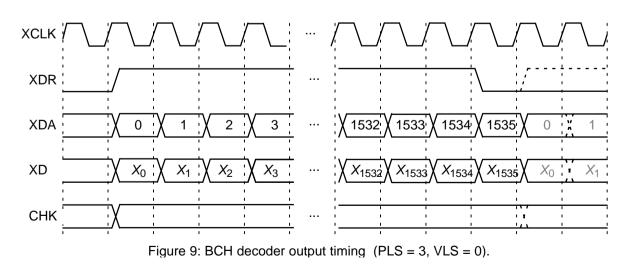

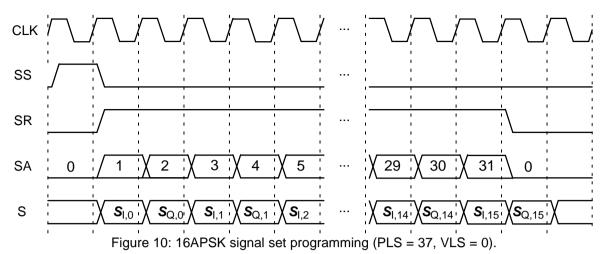

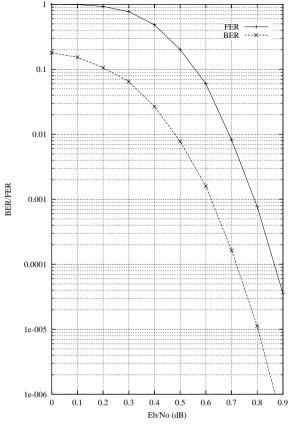

| 16       4+12APSK       3.5         17       4+12APSK       3.1         18       4+12APSK       3.6         19       4+12APSK       3.2         20       4+12APSK       3.32         21       8+8APSK       2.19         22       8+8APSK       2.42588         23       8+8APSK       2.30268         24       4+12+16rbAPSK       2.85 5.55         25       4+12+16rbAPSK       2.84 5.54         26       4+12+16rbAPSK       2.6 2.99 5.6         27       4+8+4+16APSK       2.6 2.86 5.6         29       4+8+4+16APSK       2.83 .08 5.6         30       16+16+16+16APSK       1.88 2.72 3.95         31       8+16+20+20APSK       2.2 3.6 5.2         32       8+16+20+20APSK       2.2 3.5 5.0                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 14                                             | 2+4+2APSK        | 6.39 8.0        |  |  |  |  |  |  |  |  |  |  |